DIRECT DIGITAL SYNTHESIZERS (DDS)

SYNTHETISEURS DIGITAUX A SYNTHESE DIRECTE

F6EHJ

L’apparition des DDS est en train de

révolutionner le monde des télécommunications et ouvre aux amateurs des

perspectives jusqu’alors inaccessibles.

L’objet de cet article est d’approcher

(d’apprivoiser) progressivement les DDS par leur mise en oeuvre dans des

applications amateurs qui ne sont pas des professionnels de l’électronique ou

de l’informatique, mais qui ont d’abord l’envie d’apprendre et qui disposent de

quelques bases, je pense notamment aux radioamateurs…

La théorie du fonctionnement ne sera abordée que

lorsqu’elle se révèlera indispensable à la mise en oeuvre.

C’est donc sous l’aspect pratique que cette article

aborde le sujet; il fournit les bases nécessaires à la réalisation d’un

générateur HF ou encore celle d’un VFO de récepteur.

Puis, seront exposés les avantages et

inconvénients (vécus) des DDS ainsi que les solutions palliatives envisagées.

Pour terminer, la réalisation pratique d’un générateur BF/HF pouvant être

utiliser en VFO ou même émetteur CW QRP sera décrite en détail avec les schémas

et plans des circuits imprimés.

1. Qu’est ce qu’un DDS:

Pour faire simple, je dirai que c’est une “

petite boîte noire” qui permet de générer un signal sinusoïdal à fréquence

variable avec une très grande stabilité alliée à une très grande résolution,

c’est à dire avec des incréments de fréquence très faibles.

Le terme sinusoïdal est cependant inexact car le

signal de sortie est issu d’un convertisseur digital/ analogique 10 bits.

Aussi, la forme du signal est une succession de paliers formant une sinusoïde.

L’observation à l’oscilloscope ne permet pas de discerner ces paliers, mais ils

existent et nous y reviendrons.

La définition du DDS pourrait être en quelque

sorte celle d’un VFO Geloso, encore utilisé de nos jours ou encore d’un

oscillateur type Colpitts ou Hartley avec la stabilité en moins...

Plus près de nous, le PLL avec ses parfois

capricieuses boucles de verrouillage de phase

Voyons chacune des caractéristiques énoncées.

1.1.

La stabilité:

Le DDS requiert une horloge de référence pour

élaborer son signal de sortie. La stabilité du signal généré par le DDS

reposera entièrement sur ce signal d’horloge. Ce signal sera fourni par un

oscillateur à quartz.

Si l’on prend comme exemple un signal de

référence de 125 MHz et un signal de sortie du DDS de 12.5 MHz, une dérive de

10 Hz de l’horloge affectera le signal utile de 1Hz… !

1.2. Fréquence du signal:

La fréquence de l’oscillateur à quartz qui

pilote le DSS est dépendante de deux paramètres:

- la fréquence maximale admissible par le DDS

lui-même

- la fréquence maximale du signal souhaité.

Bien que la fréquence théorique utile (Nyquist)

soit égale à la moitié de la fréquence de l’horloge on prendra comme règle de

base : fréquence de l’oscillateur égale ou supérieure à 3 fois la

fréquence maximale de sortie désirée.

Cette règle simple permet alors de choisir a

priori le DDS qui convient.

Quelques exemples:

- Soit à remplacer le VFO d’un transceiver dont

la stabilité et la précision de fréquence sont jugés insuffisantes.

Le VFO fournit un signal entre 5 et 5.5 MHz.

La fréquence haute est donc 5.5

MHz, un oscillateur de 16.5 MHz est le minimum autorisé, un DDS acceptant un

signal d’horloge à 15/20 MHz sera retenu en configuration minimale.

- Soit un transceiver couvrant les bandes

amateur (1.8/29.7 MHz) possédant un seul changement de fréquence avec une Fl à 9MHz.

Dans ce cas, le VFO doit couvrir la plage de

10.8 à 38.7 MHz. C’est déjà beaucoup plus difficile pour un VFO classique.

Dans ce cas, la fréquence de l’oscillateur du

DDS devra être au minimum de 38.7x3 soit 106.1 MHz, ce qui nécessite un DDS

acceptant 100 MHz. Ce dernier exemple peut également être appliqué pour un

récepteur à conversion directe requérant un VFO de 0 à 29.7 MHz; la fréquence

de l’horloge se retrouve alors à 90 MHz.

Cependant, comme règle

générale, plus la fréquence utile sera éloignée de la fréquence maximale du

DDS, meilleure sera la qualité du signal.

Les DDS récents admettent des signaux d’horloge

à 125 , 180 voire 300 MHz, ce qui permet d’obtenir des signaux utiles jusqu’à

100 MHz.

Malheureusement, leur disponibilité en petite quantité et leur prix ne

permettent pas toujours à l’amateur de se lancer dans des montages requerrant

leur utilisation.

Afin de pouvoir appliquer ce qui sera

exposé, le DDS AD9850, disponible chez les revendeurs sera le seul utilisé.

1.3. Résolution:

La résolution est l’incrémentation minimal de la

fréquence du signal de sortie.

Elle dépend directement de la fréquence de

l’horloge et du DDS lui-même.

Pour une fréquence d’horloge de 125 MHz, la

résolution disponible est égale à.. 0.0291 Hz I

1.4. Conclusion:

Obtenir un signal de fréquence variable entre 0

et 40 MHz, par pas de 0.0291 Hz minimum possédant la stabilité d’un quartz.. On

est bien proche de l’oscillateur idéal.

Cet oscillateur est maintenant à notre portée.

Profitons en!

2. Mise en oeuvre:

Il ne faut pas s’attendre à trouver des selfs et

des condensateurs variables avec le DDS: le DDS est un composant qui requiert

très peu d’éléments externe : dans le montage proposé, seuls 3 résistances et 4 condensateur de découplage

seront nécessaires pour le DDS.

Par contre, il ne se commande pas très

simplement, il faut en fait lui parler afin de lui ordonner ce qu’il faut

faire.

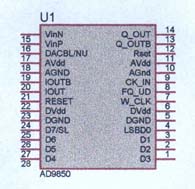

2.1. Le boîtier:

Il s’agit, vous l’aurez tous deviné, d’un

circuit intégré a nombre de pattes variable, pour ceux que je connais, entre 16

et 44.

Comme indiqué précédemment, nous nous bornerons

à retenir un seul modèle fabriqués par Analog Device: l’ AD 9850.

Une parenthèse cependant : l’AD9835 est un modèle plus rustique admettant

une fréquence d’horloge de 50 MHz ; l’AD9851 est au contraire plus

performant (180 MHz) mais ces deux composants restent quasiment introuvables.

L’AD9850 possède 28 pattes. Autant dire de suite

qu’une des difficultés est la taille de la bête car ce sont des boîtiers SSOP

ou “ultra small SSOP”. Ca promet et ce n’est rien de le dire...!

La taille hors tout est de l’ordre de 10mm X

7mm, la distance entre patte de 1mm !

2.2. L’ AD 9850:

C’est le premier DDS que j’ai utilisé et sa mise

en œuvre est à la portée de l’amateur

moyen comme l’auteur.

Ce DDS admet une horloge à 125 MHz ce qui

décline un signal de sortie de fréquence maximale autour de 40 MHz.

Après essai, il est possible d’aller au-delà et

il monte à 170 MHz; par contre la consommation augmente rapidement et la

température également.. Je n’ai pas insisté outre mesure.

Le pas minimal d’incrémentation est de 0.03 Hz

avec l’horloge à 125 MHz, la tension de sortie de 1.2V efficaces sur 50 ohms

entre 0.03 Hz et 40MHz....

2.2.1. Les différentes

PIN:

Elles sont au nombre de 28, mais beaucoup

d’entre elles ne sont pas utilisées ou reliées à la masse ou à l’alimentation, il

en résulte que seules les pins suivantes méritent une description:

PIN 7:W_CLCK

C’est la broche qui reçoit l’horloge de travail.

Cet horloge va cadencer le chargement du message « fréquence »

du DDS

PIN8:FQ_UD

Cette broche valide la fin du message de

programmation et indique au DDS qu’il peut prendre en compte ce qui vient

d’être chargé.

PIN 9:CLK_ IN

C’est l’entrée de l’oscillateur de référence à

quartz évoquée ci-avant.

PIN 25: SERIAL DATA IN

Cette entrée reçoit le message de programmation

fréquence.

PIN

21: out

C’est la sortie analogique du DDS (la plus

intéressante...!)

PIN 22: out B

C’est la même que ci-dessus, déphasée de 180°

PIN 11 et 18 : Avdd

Il s’agit de l’alimentation 5V de la partie

analogique

PIN 6 et 23 : DVdd

Il s’agit de l’alimentation +5V de la partie

digitale.

Les autres pins sont soient à la masse, soient

inutilisées et restent en l’air.

Pour mémoire les pins 2, 3 et 4 qui

sont trois des entrées parallèles servent à configurer le DDS en mode série.

Remarques

sur les alimentations :

Comme décrit ci-dessus, le 9850 requiert deux alimentations +5V : une pour

sa partie digitale et une pour sa partie analogique. Ceci complique le dessin

du circuit imprimé et nécessite un filtrage séparé des deux sources 5V.

Il est possible de s’en affranchir en ignorant cette particularité et en

alimentant les 4 pins par le +5V.

La contre partie de cette simplification est l’accroissement de signaux

parasites en sortie du DDS.

En fonction des besoins en pureté

spectrale, on optera pour l’une des deux solutions.

Dans tous les cas, le découplage des 4

pins d’alimentation (6, 11, 18, 23) sera soigneusement réalisé au ras de chaque

pin. Des condensateurs chip de 10 à 100 nF seront de préférence employés.

Pour conclure sur cette énumération, on s’aperçoit que tout compte fait, elle

n’est pas très longue et qu’il n’y a pas lieu de s’affoler…

2.2.2. PRINCIPE DE FONCTIONNEMENT:

Il est indispensable de comprendre ce

qu’il est nécessaire de faire avant de démarrer.

Trois étapes sont nécessaires :

1. Elaboration de la fréquence désirée:

La génération de fréquence repose sur le chargement d’un registre à 32 bits

situé dans le DDS.

Ce mot de 32 bits (4 octets) est entièrement représentatif de la fréquence du

signal de sortie.

Il est donc nécessaire de le définir,

de le générer et de le charger dans le DDS. Ces 3 opérations sont

les seules (ou presque) à réaliser.

2. Définition du message fréquence

32 bits:

Il est défini par la formule suivante:

F out= Fxtal X N/2exp 32 (Fxtal =

fréquence de l’oscillateur horloge)

On en déduit simplement N :

N= Fout x 2exp 32 / Fxtal

Exemple: Soit à générer un signal de sortie de 5.250 023 MHz avec un DDS muni

d’un oscillateur d’horloge à 100 MHz

N= 5250023 Hz x 4294967296/100 000 000 =

225 488 771

Cette valeur est à convertir en hexadécimal, soit 0D 70 A7 B3. On complète avec

des zéros si nécessaire afin d’obtenir les 32 bits requis. C’est tout.

Voir le tableau Excel en

exemple

3. Génération du message de 32 bits:

Ce message de 4 octets va devoir prendre

une consistance logique car pour l’instant, il n’est que le résultat d’un

calcul arithmétique.

A ce stade, il est nécessaire de

comprendre comment il va falloir s’adresser au DDS pour lui faire connaître ce

message (notre objectif).

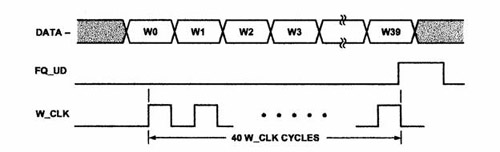

Pour entrer le message dans le DDS, deux

solutions s’offrent à nous:

Le mode parallèle:

Le mode parallèle:

Le DDS

possède 8 entrées (8 fils correspondant chacun à un bit d’un octet). Comme le

mot “fréquence” comporte 4 octets (32 bits), le DDS accepte que l’envoi se

fasse en 4 fois, c’est à dire un octet après l’autre.

Par contre, il demande que ce soit

l’octet de poids faible qui soit présenté en premier. Si l’on reprend l’exemple

calculé précédemment, les différentes octets à charger vont se présenter ainsi:

Mot de 32 bits: 0D 70 A7 B3

Hex Binaire

1er octet: B3 1011 0011

2ème octet: A7 1010 0111

3ème octet: 70 0111

0000

4ème octet 0D 0000 1101

Ceci est juste pour mémoire car ce n’est pas ce mode que nous utiliserons car

il requiert un bus complet de 8 bits, denrée particulièrement rare dans les

microcontrôleurs récents bon marché.

Le mode série

Cette fois, c’est le bon...’

L’entrée se fait sur un seul fil et

c’est suffisant puisque les 32bits vont se succéder à la queue-leu-leu. C’est

le rôle de l’entrée SERIAL_DATA_ IN pin 25.

Le DDS demande également à ce que le premier bit

soit de poids le plus faible.

Si l’on reprend le résultat trouvé précédemment,

le message est le suivant en partant de la gauche:

11001101 00010101 00001110 1011000

Noter l’ordre des bits, poids faible de l’octet

de poids faible en premier.

Par contre, l’envoi des bits ne doit pas se

faire n’importe comment : il est nécessaire de les synchroniser avec une

horloge. Ce signal sera appliqué sur l’entrée W_CLK pin 7.

Non seulement l’envoi des bits doit être

synchronisé avec l’horloge de travail, mais encore faut il prévenir le DDS

quand le chargement commence et à quel moment il peut prendre en compte

celui-ci.

Il faut en effet que la totalité des 32 bits ait

eu le temps d’arriver dans le registre fréquence...

C’est le rôle de l’entrée FQ_UD qui recevra un

signal en début et en fin de chargement.

A l’issue de ce processus qui va demander

quelques microsecondes, la fréquence correspondante sera disponible en sortie.

C’est tout… !

3.

INTERFACAGE DU DDS

Toutes les opérations énumérées ci-dessus vont devoir être réalisées de

très nombreuses fois : par exemple à chaque mouvement du « bouton

fréquence » d’un VFO, donc elles doivent être automatisées et effectuées dans

un temps minimal.

Les 32 bits, le signal d’horloge de travail et

le signal de validation vont devoir être générés et l’opération sera terminée

pour la fréquence définie.

Le recours à la logique câblée TTL/MOS pourrait

être une des solutions mais le nombre de fréquences différentes serait vite

limité. Aujourd’hui la technologie nous offre des opportunités beaucoup plus

performantes permettant une très grande souplesse de fonctionnement.

Je veux parler ici des microcontrôleurs. Le mot

est lâché et il va falloir faire avec ces nouveaux composants qui deviennent

rapidement indispensables!

3.1.

LE MICROCONTROLEUR:

Je ne parlerai ici que de la famille des PIC de

Microchip qui sont les seuls µcontrôleurs que j’ai expérimentés.

Pour faire simple, nous prendrons le plus simple

- mais pas le moins performant de la famille- je veux citer le PIC 16F84.

L’intérêt de ce composant est d’abord son coût

(7€ environ) et sa capacité à posséder une mémoire flash c’est à dire

programmable et effaçable à volonté de 1 Koctet environ (1024 mots de 14 bits

en réalité).

Le PIC possède 13 entrée/ sorties réparties en 5

fils pour le port A (RA0 à RA4) et 8 fils pour le port B (RB0 à RB7).

Je passe sous silence les fonctions

complémentaires (timer, interruption...) dans l’immédiat.

Cette pléthore d’entrées /sorties va être

largement suffisante pour commander le DDS qui ne requiert que 3 fils.

Par contre, si l’envie nous prenait de disposer

d’un affichage digital de la fréquence de sortie, les autres E/S nous serait

d’un grand secours.

Si par ailleurs, il était nécessaire de changer

la fréquence du DDS (pour recevoir des stations différentes par exemple dans le

cas d’un VFO), encore une fois les E/S seraient les bienvenues pour gérer un

codeur mécanique ou optique par exemple.

J’arrête la l’énumération car je suis persuadé

que ça vous donne des idées...!

D’autre part, le PIC lui aussi requiert un

signal d’horloge qui peut être fourni par un quartz ou un simple réseau RC. Une

alimentation +5V permet d’alimenter le PIC (quelques mA).

Dans l’immédiat on en reste au DDS dans sa mise

en oeuvre la plus simple.

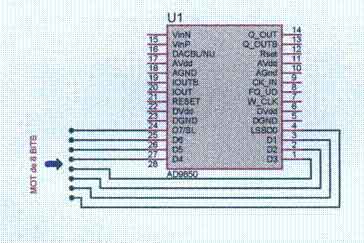

3.2.

INTERFACAGE MATERIEL DDS/ µcontrôIeur:

Il faut donc relier le DDS avec le PIC.

Comme évoquée à l’instant, cette liaison est des

plus simple puisque 3 fils de commande sont seulement nécessaires pour piloter

le DDS:

SERIAL_DATA vers

RA0

W_CLK vers RA1

FQ_UD vers RA2

Le choix des trois ports RA0 à RA2 est

complètement arbitraire, on décide ce que l’on veut parmi les ports

disponibles.

La platine d’essai

se présente alors sous cette forme:

On remarquera quelques points

particuliers :

- Les alimentations :

A partir d’une source 15 à 18V (petit bloc secteur), deux régulateurs

fournissent le +12 et le +5V.

L’alimentation +12V est uniquement destinée à l’amplificateur de sortie.

L’alimentation +5V est séparée en deux pour fournir le +5V aux parties

analogique (+5A) et digitale (+5D). On notera les condensateurs C4 à C7 qui

seront placés près des fils d’alimentation du 9850.

- Les liaisons PIC/DDS :

Pour ne pas charger le schéma, les

fils entre le PIC et le DDS ne sont pas figurés. Il suffit de repérer les

entrées sorties de l’un et de l’autre pour « visualiser » les

connexions.

Autant dire que ce schéma n’autorise aucune

commande externe pour faire varier la fréquence ni son affichage. Il pourra

être cependant utilisé pour réaliser un oscillateur à fréquence fixe dont la

valeur pourra cependant être changée ou ajustée selon le besoin.

3.2.

LOGICIEL:

Evidemment, il faut en passer par là. Ce n’est

pas bien compliqué, puisque j’y suis arrivé sans vraiment être un spécialiste,

ni tombé dedans tout petit.

L’éditeur utilisé est MPLAB, l’assembleur est MPASM disponible tous deux en

libre service sur le site Microchip. Attention les fichiers ont une taille

respectable…

Que faut-il faire? Résumons les différentes

étapes:

3.2.1. générer les 32 bits, soit 4 octets.

Il n’y a pas plus simple. Il suffit de charger

le contenu des 4 octets (hexa) dans 4 emplacements mémoire que l’on aura

définis préalablement. Nous les appellerons ACCO, ACC1, ACC2 et ACC3. On en

prendra un cinquième ACC4 qui sera toujours à zéro pour faire plaisir au DDS

afin de ne pas le désorienter...! (en réalité ce 5ème octet permet

de commander la phase du signal de sortie, sans intérêt pour notre

application).

Pour l’exemple, la valeur retenue sera chargé

dans ces variables dès l’initialisation du PIC par la fonction “define”:

define ACCO h’B3’

define ACC1 h’A7’

define ACC2 h’70’

define ACC3 h’0D’

define ACC4 0

Voilà, c’est fait une fois pour toute ;

pour changer de fréquence, il faudra modifier ces valeurs, manuellement pour

l’instant.

3.2.2.

créer l’horloge de travail:

Il n’y a pas plus simple. ..Nous avons décidé que

l’entrée W_CLK du DDS serait attaquée par RA1

Il suffit de mettre alternativement ce bit à 1

puis à 0 pour créer un magnifique signal carré en sortie de RA1.

Deux instructions pour cela sont nécessaires:

BSF RA1 (Bit Set variable) met le bit de RA1 à 1

BCF RA1(Bit Clear variable) met le bit de RA1 à 0

Pour recommencer, il suffit de se repositionner

à la première instruction.

3.2.3.

créer le signal de validation:

C’est identique à ci-dessus. Nous avons choisi

RA2 pour attaquer l’entrée FQ_UD du DDS. Les deux instructions utilisées

précédemment vont remplir le même rôle.

BSF RA2

BCF RA2

3.2.4. envoi des 32 bits:

comme nous l’avons vu tout à l’heure, le

microcontrôleur ne peut traiter que des octets, ses registres étant limités à 8

bits. C’est la raison pour laquelle nous avons découpé le mot de 32 bits à

destination du DDS en 4 octets (ACC0. . .ACC3). Il sera donc nécessaire de

charger séquentiellement ces 4 octets en commençant par le bit le moins

significatif (LSB) de l’octet de poids le plus faible.

En interne du microcontrôleur, les bits sont

dans les registres mémoire ACC0..ACC3 de 8 bits, il sera donc nécessaire des

les sortir un par un, puis de les envoyer l’un

après l’autre vers le DDS.

L’ opération de chargement doit se faire en

synchronisme avec l’horloge de travail et le signal de validation.

Ceci ne complique pas vraiment la procédure mais

nécessite de séquencer les différents évènements et particulièrement l’horloge

et les données.

Le DDS prend en compte la donnée (1 bit du

message) sur un front montant de l’horloge de travail.

La procédure globale est la suivante:

- lire l’octet de poids faible ACC0

- décaler l’ensemble des bits vers la droite

cette opération permet de récupérer le bit

‘sortie de l’octet’ dans un bit d’un registre spécifique du µcontrôleur: la

carry (ou retenue). Cette carry contiendra donc alors le bit à envoyer au DDS

dont la valeur sera...binaire, 1 ou 0.

- faire monter l’horloge de travail à 1

- mettre l’horloge de travail à 0

Voilà pour le premier bit. Il faut refaire

l’opération 32 fois, sachant que tous les 8 bits, il faudra changer d’octet

(ACCO puis ACC1 .. ..ACC3).

Voyons en détail le sous programme ci-dessous:

|

LDBYTE |

|

C’est le nom (étiquette) du sous-programme

qui permettra de l’appeler |

|

|

|

|

|

|

MOVLW 8 |

Pour charger un octet bit par bit,

il faut faire l’opération 8 fois. On se servira d’un compteur de bit

initialisé à la valeur 8. |

|

|

|

|

|

|

MOVWF COUNT |

Le

registre W étant utilisé en permanence pour les besoins internes du µ, on se

dépêchera de transférer le contenu de W dans un registre temporaire

mémoire : COUNT |

|

|

|

|

|

|

BCF W_CLK |

Instruction décrite précédemment,

l’horloge de travail est mise à O |

|

BIT |

BCF DATA |

La sortie DATA (entrée SERIAL du

DDS) est mise à zéro |

|

|

RRF TEMP,1 |

L’octet contenu dans TEMP est décalé

d’un rang vers la droite et tombe dans la CARRY |

|

|

BTFSC CARRY_BIT |

Voyons le contenu de la CARRY (1

ou 0). Si 1 on passe à l’instruction suivante (BSF DATA), sinon on la saute

pour aller directement à BSF W CLK |

|

|

BSF DATA |

Si 1 on met le data à 1 sinon on

ne fait rien data=0 puisqu’il est déjà à 0 |

|

|

BSF W_CLK |

On fait monter à 1 le signal de

l’horloge de travail. |

|

|

BCF W_CLK |

On le fait redescendre pour

terminer le c cie |

|

|

DECFSZ COUNT,1 |

Le 1er bit a été envoyé, on

décrémente le compteur de bit |

|

|

GOTO BIT |

Et on retourne charger le bit

suivant à l’étiquette BIT pour l’instruction BCF _DATA |

|

|

RETURN |

Tant que le compteur de bit n’est pas

à 0, on continue à charger les bits les uns après les autres. Les 8 bits

chargés, on passe à l’octet suivant. |

Afin d’économiser les variables (la place

mémoire), les 4 octets seront tour à tour transférés dans une variable temporaire

TEMP qui sera utilisée par le programme précédent LDBYTE. C’est le but du

sous-programme suivant :

|

LD9850 |

|

|

|

|

MOVF ACCO,W MOVWF TEMP CALL

LDBYTE |

transfert ACCO dans le registre W transfert

W dans TEMP appelle le S/P de chargement d’un octet |

|

|

|

|

|

|

MOVF ACC1 ,W MOVWF TEMP CALL

LDBYTE |

transfert ACC1 dans le registre W

transfert W dans TEMP appelle le S/P de chargement d’un octet |

|

|

|

|

|

|

MOVF ACC2 ,W MOVWF TEMP CALL

LDBYTE |

transfert ACC2 dans le registre W

transfert W dans TEMP appelle le S/P de chargement d’un octet |

|

|

|

|

|

|

MOVF ACC3 ,W MOVWF TEMP CALL

LDBYTE |

transfert ACC3 dans le registre W transfert

W dans TEMP appelle le S/P de chargement d’un octet |

|

|

|

|

|

|

MOVF ACC4 ,W MOVWF TEMP CALL

LDBYTE |

transfert ACC4 dans le registre W

transfert W dans TEMP appelle le S/P de chargement d’un octet |

|

|

|

|

|

|

BSF FQ_UD |

|

|

|

BCF FQ_UD |

|

|

|

RETURN |

|

Une fois les 4 octets(S) sérialisés bit par bit

(32/40), il ne reste plus qu’à signaler au DDS que l’opération est terminée en

faisant monté le signal FQ_UD à 1. On n’oublie pas de le remettre à 0 pour être

prêt la fois suivante.

..

BSF F0_UD set

Iatch pulse

BCF

FQ_UD reset

latch pulse

Il ne reste plus qu’à introduire ce programme

dans le PIC (le programmer) et dès le reset, le programme s’exécutera en

quelques microsecondes.

Le DDS doit alors générer la fréquence de 5, 250

023 MHz.

Bon, ce n’est pas extrêmement simple mais ce

n’est pas bien compliqué. Ce module est le coeur du chargement du DDS et si ce

n’est pas le seul moyen d’y arriver, cette solution est très souple.

Evidemment, ce programme atteint rapidement ses

limites car la fréquence générée ne peut être changée que par altération

manuelle des 4 variables ACCO à ACC3. Ce serait bien de pouvoir la faire varier

facilement par une commande accessible, un bouton par exemple...

Par ailleurs, il serait agréable de connaître la

fréquence de sortie car même si on se souvient du contenu des 4 octets, à moins

de parler hexadécimal couramment et de faire les conversions octets / fréquence

instantanément, il sera difficile de la mémoriser.

4. L’AFFICHAGE DE LA

FREQUENCE:

C’est une nouvelle étape, pas plus complexe.

Pour rester dans des coûts abordables tout en

bénéficiant d’un affichage correct, mon choix s’est porté sur un afficheur à

cristaux liquide (LCD) de 2 lignes de 16 caractères chacune.

Il en existe de nombreux modèles et celui que

j’utilise couramment est produit par

HITACHI.

Il possède

son gestionnaire d’entrées/ sorties et le générateur de caractères est intégré

et programmable (je l’ai utilisé tel quel).

Interfaçage:

L’afficheur qui comporte 16 broches nécessite 11

fils pour sa commande:

- un bus de donnée de 8 fils (1 octet)

- un fil

RS (selecteur de registre)

-

un fil E (enable)

-

un fil R/W qui ne sera pas utilisé

Les 5 autres fils sont utilisés pour l’alimentation,

le contraste et la masse. Certains modèle un peu plus coûteux possèdent un

rétro-éclairage bien pratique en lumière ambiante insuffisante qui mobilisent

alors les deux fils restants.

La commande d’un tel afficheur n’est pas des

plus simple et je ne m’étendrais pas davantage dessus car ceci présente peu

d’intérêt.

Une des difficultés majeure est due à la lenteur

de ce composant qui nécessite d’attendre entre chaque commande, sous peine

d’échec.

A savoir que l’on trouve des sous-programmes tout

prêt qu’il suffit d’adapter (avec plus ou moins de bonheur parfois) à la

configuration matérielle utilisée. Pour ma part, j’ai entièrement réécrit cette

partie.

Par ailleurs, compte tenu du faible nombre de port disponible sur le

microcontrolleur, il est souvent nécessaire d’avoir recours à une extension

hardware qui permet de commander l’afficheur avec seulement 3 fils. C’est le

rôle du 74HC595 utilisé ici.

L’insertion de ce composant permet d’économiser

les ports d’entrée/ sortie mais la complexité du logiciel s’accroît un peu.

Ces 3 fils seront :

- SERIAL DATA IN (on n’invente rien)

- CLK_595 (c’est la W_CLK du DDS..)

- LATCH (c’est le FQ_UD du DDS…)

Rappelons à ce moment, que pour le DDS, en

l’absence de signal FQ_UD, les données chargées ne seront pas prises en compte,

c’est comme si rien n’avait été envoyé.

Pour le 595, la règle est la même: tant que

LATCH n’est pas activé, les données chargées sont inutiles.

Dans cette configuration, rien ne nous empêche

de faire transiter les données (SERIAL_DATA_IN) à destination du DDS ou du 595

par le même fil...!

5. LA COMMANDE DE LA

FREQUENCE :

Bien évidemment, disposer d’une seule

fréquence présente peu d’intérêt, la

commande de variation de la fréquence doit donc pouvoir être faite manuellement

par l’utilisateur et à sa guise.

Cette variation de fréquence se caractérise par trois paramètres :

5.1.

La plage ou les plages de fréquences à couvrir :

Dans l’hypothèse d’un VFO, cette plage pourra

par exemple être limitée de 5.0 à 5.5 MHz.

Dans l’hypothèse d’un générateur HF, cette plage

sera beaucoup plus importante : # 0

à 40 MHz par exemple.

Dans la dernière hypothèse de l’oscillateur

local d’un récepteur OM, il faudra considérer une excursion de fréquence de 500

kHz par bande, soit 9 plages (voire plus).

5.2.

Le pas

C’est la variation de fréquence par « tour

de bouton ». Plus précisément, c’est la valeur de l’incrément unitaire de

fréquence.

Cet incrément dépendra de l’utilisation du DDS et pour un VFO par exemple, la

tentation sera grande de viser un incrément très faible. Une valeur de 1Hz

semble souvent paraître idéale.

A ce stade, il faudra prendre en compte les conséquences d’un tel choix ;

en effet, une excursion de 1kHz (ce qui est peu), impliquera 1000 chargements

du DDS en quelques secondes ou millisecondes ! On voit qu’alors le

microcontrôleur aura fort à faire et il n’est pas certain qu’il puisse assumer

cette lourde tâche en si peu de temps.

On le constate quelques fois sur certains équipements ou le vernier fréquence

semble « patiner » lorsqu’il est rapidement actionné (vérifiez sur

votre transceiver…. !) conséquence : il faudra trouver le compromis

qui satisfasse l’utilisateur tout en conservant une marge au microcontrôleur.

Dans la pratique, un pas de 10Hz est généralement considéré comme

« standard » et à cette valeur d’incrément, la note d’un signal CW

est réglée sans discontinuité à l’oreille.

Le corollaire

d’une faible valeur de pas est l’excursion de larges plages de

fréquences. Si l’on considère un pas de 10 Hz et 20 pas par tour de bouton,

soit 200Hz par tour, 2500 tours de bouton seront nécessaires pour balayer une

plage de 500 kHz…. ! C’est beaucoup.

Dans ce cas, il sera préférable de passer à une valeur supérieure du pas :

100 Hz, 1kHz, voire 10kHz.

5.3.

La préselection :

Elle devient nécessaire pour couvrir des plages

de fréquences faibles, éloignées les unes des autres ; c’est typiquement

le besoin d’un oscillateur local couvrant les 100 à 500 kHz des bandes amateurs

(3.5 à 3.8, 7 à 7.1 etc…).

Dans ce cas, il sera judicieux de pouvoir caler

le début de l’excursion en début de bande afin

de ne pas avoir à balayer les inter-plages.

Il pourra en être de même pour un générateur HF destiné au réglage d’un

récepteur couvrant les seules bandes amateurs.

On voit donc qu’en plus de la commande de la

fréquence proprement dite, deux commandes seront nécessaires : pas et

bandes. Des boutons poussoirs rempliront parfaitement cette fonction et feront

appel aux interruptions du PIC.

6. MESURE OU GENERATION

DE LA FREQUENCE ?

De prime abord, on pourrait opter pour une

mesure de la fréquence issue du DDS et son affichage direct. C’est la solution

utilisée jadis lors de l’apparition des premiers VFO digitaux.

Elle nécessite la mise en œuvre d’un compteur / fréquencemètre, pas obligatoirement

évidente à implanter dans le microcontrôleur ou à part.

Il est aussi possible de fonctionner en aveugle : on se cale sur une

fréquence initiale et ensuite on compte le nombre de pas envoyés au DDS. Il

suffit d’incrémenter simultanément la valeur de l’affichage du pas courant.

Cette solution (que j’ai utilisée) à un inconvénient majeur : celle d’être

inexacte. En effet, le pas DDS n’est jamais

un nombre entier (rappelez-vous la formule). Par contre, l’incrémentation de

l’afficheur est toujours une valeur

entière (un digit). Aussi, après un certain nombre de pas, il s’introduit un

décalage entre la fréquence issue du DDS et celle affichée et ceci

proportionnellement au nombre de pas effectués depuis la fréquence de départ.

La différence peut ne pas être très importante mais elle s’avère gênante car la

fréquence affichée n’est jamais exacte….

La solution est de prendre le problème à l’envers ! On affiche d’abord la

fréquence puis on la convertit en valeurs DDS.

Ce n’est pas vraiment compliqué car il suffit alors de prendre le poids

individuel de chaque digit (10Hz, 100Hz, 1kHZ …) et de le multiplier par

la valeur affichée.

Le poids de chaque digit sera initialisé une

fois pour toute en fonction de l’horloge DDS. Pour une horloge à 125 MHz on

aura par exemple :

10Hz 01

58

100Hz 0D 6C

1kHZ 86 37

10Khz 05 3E 29

100kHz 34

6D 9C

1MHz 02

0C 48 13

10MHz 14

7A D0 BF

En supposant que la fréquence lue sur l’afficheur soit de 14 001.73 kHz, la

formule suivante fournit les 4 octets nécessaires au DDS :

3(01 58)+7(0D 6C)+(86 37)+4(02 0C 48 13)+(14 7A

D0 BF)

Cette opération sur 32 bits n’est pas des plus simples avec un microcontrôleur

8 bits mais on y arrive !

A ce stade, on a donc généré un signal DDS égal à la fréquence affichée et ce

n’est déjà pas si mal. Pour un générateur HF c’est suffisant, pour un

oscillateur local ou un VFO, ce n'est pas terminé...

Eh oui, la fréquence de l’oscillateur local ou du VFO n’est jamais égale à la

fréquence à recevoir…(sauf pour la conversion directe). Il va donc être

nécessaire de décaler la fréquence du DDS d’une « certaine » valeur…

Calcul de la valeur de décalage (Offset)

On prendra pour exemple une FI à 5645 kHz. Dans

ce cas, la fréquence de l’oscillateur local générée par le DDS pourra être

supérieure ou inférieure de 5645 kHz à la fréquence affichée.

Il suffit alors de soustraire ou d’ajouter la valeur 5645 kHz (BE 91 8F 0B) à

la valeur afficheur avant de la charger dans le DDS.

En réalité….ce n’est pas si simple car il faudra tenir compte de la bande

latérale utilisée !

Dans l’utilisation d’un filtre FI unique, la réception de l’une ou l’autre des

bandes latérales s’effectue par changement de la fréquence du BFO, fréquence

que l’on place de part et d’autre des fréquences de coupures du filtres. Il en

résulte un décalage qui se traduisait jadis par la présence de deux repères

distincts sur le vernier des fréquences.

Si l’on souhaite conserver un affichage exacte de la fréquence générée par le

DDS, il est donc nécessaire de se décaler en fonction de la bande latérale

reçue. En fait, « c’est comme si » la fréquence du filtre FI

changeait.

Pour l’exemple considéré, on trouve 5645 kHz pour USB et 5642.060 kHz pour LSB.

Ces deux valeurs seront donc additionnées ou soustraites avant chargement du

DDS.

Dans l’hypothèse d’un second changement de

fréquence, le principe est identique, seul un oscillateur fixe supplémentaire

pour descendre de la première à la seconde FI est nécessaire.

Par contre, le décalage reste le même.

A l’issue des opérations détaillées précédemment,

on dispose d’un VFO dont, la fréquence affichée est égale à la fréquence

générée plus ou moins les fréquences BFO (et inversement) quelque soit la bande

latérale utilisée.

Autant dire que le plus gros est fait…. !

Sans le décalage FI on dispose d’un oscillateur

pour récepteur à conversion directe ou encore d’un générateur HF, sachant que

seule la programmation du microcontrôleur est à adapter en fonction du besoin.

Cette programmation pourra être également adaptée à la fréquence FI utilisée

(10 .7 MHz, 9MHz, 4.9 MHz, 455 kHz..) pour ne citer que les plus

courantes, toutes les valeurs pouvant évidemment être prise en compte.

A ce propos, il faudra cependant prendre en compte les limites du DDS annoncées

précédemment, à savoir que la fréquence de sortie maximale sera égale à F

Horloge /3, soit 40 MHz pour une horloge à 125 MHz.

On s’aperçoit alors que l’utilisation d’une FI à 10.7 MHz amène le DDS à 40 MHz

pour la bande 10 mètres. Si la bande 50 MHz était visée, il faudrait préférer

le mélange soustractif (50-10.7) afin de rester à l’intérieur de la plage de

fréquence « utile » du DDS.