|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

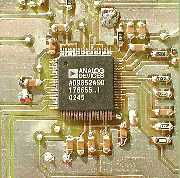

EXPERIMENTATION AVEC UN DDS AD9852 REALISATION D'UN GENERATEUR 0 à 120 MHz (et plus) 1. PREAMBULE Cet article fait suite aux premiÃres expÃĐrimentations rÃĐalisÃĐes et dÃĐcrites dans la revue (DDS : Direct Digital Synthesizers) Comme indiquÃĐ prÃĐcÃĐdemment, les DDS permettent la rÃĐalisation dâ??oscillateurs de trÃs grande stabilitÃĐ (celle du quartz) et de trÃs grande rÃĐsolution (<0.1 Hz). Par contre la puretÃĐ spectrale nâ??est pas toujours garantie, particuliÃrement dans les rÃĐalisations requÃĐrant une grande excursion de frÃĐquence avec un pas dâ??incrÃĐmentation faible. On citera en exemple les applications amateurs dÃĐcamÃĐtriques. Cet article propose des solutions permettant de pallier les dÃĐfauts rencontrÃĐs et en application la description (peut-Être inÃĐdite) d'un gÃĐnÃĐrateur couvrant la gamme audio à 120 MHz. 2. PURETE SPECTRALE DES DDS La puretÃĐ spectrale est directement liÃĐe à plusieurs facteurs maÃŪtrisables, sachant quâ??ils en existent dâ??autres bien plus difficile à cerner : 2.1. la frÃĐquence de lâ??horloge du DDS La rÃgle de base est que la frÃĐquence du signal de sortie nâ??excÃde pas 40% de la frÃĐquence de lâ??horloge. Cette rÃgle est simpliste car elle permet de rester suffisamment ÃĐloignÃĐe du mÃĐlange f horloge â?? f signal. Par exemple, prenons une horloge de 125 MHz. 40% nous amÃne à 50 MHz et le mÃĐlange à 125 -50 = 75 MHz. Avec un bon filtre elliptique à 3 cellules on attÃĐnue fortement cette raie. Mais en rÃĐalitÃĐ le principal problÃme nâ??est pas là . Il se situe principalement au moment de la ÂŦ reconstruction Âŧ de la sinusoÃŊde par le convertisseur digital/analogique (DAC). 2.2. Le convertisseur digital/analogique (DAC) : Sur les DDS courant ces convertisseurs ont une rÃĐsolution de 10 bits, ce qui nâ??est dÃĐjà pas si mal, malgrÃĐ tout, la sinusoÃŊde nâ??est pas parfaite et prÃĐsentera dâ??autant plus dâ??ÃĐchelons ou de pallier que la frÃĐquence de lâ??horloge sera faible (pour une frÃĐquence donnÃĐes en sortie) ; on aura donc tout intÃĐrÊt à utiliser le DDS au maximum de ses performances en terme de frÃĐquence dâ??horloge. Un DAC 12 bits, comme nous le verrons plus loin amÃĐliore sensiblement les choses. Mais comme mentionnÃĐe prÃĐcÃĐdemment, ce nâ??est pas là quâ??est la principale cause de signaux indÃĐsirables. Les donnÃĐes fournies au DAC sont contenues dans une table assurant la correspondance entre les donnÃĐes binaires programmÃĐes par lâ??utilisateur (frÃĐquence dÃĐsirÃĐe en sortie) et la frÃĐquence à gÃĐnÃĐrer par le DAC (en fait ce sont des donnÃĐes de phase et dâ??amplitude). Si lâ??on se rappelle que la frÃĐquence dâ??un DDS courant est codÃĐ sur 32 bits, soit 4294967296 combinaisons offrant alors avec une horloge à 125 MHz une rÃĐsolution de 0.023 Hz, on imagine la taille de la table nÃĐcessaire au DACâ?. ! Plusieurs gigaoctets seraient nÃĐcessaires et câ??est la raison pour laquelle, seules ÂŦ quelques Âŧ valeurs rÃĐsident dans cette table, les autres ÃĐtant approchÃĐes. On devine facilement alors ce quâ??il advient lorsque lâ??on gÃĐnÃre une valeur qui nâ??est pas dans la table, on prend la valeur la plus proche et on tronque les ÂŦ dÃĐcimales Âŧ (les bits de poids faible). Cette troncature a un effet dÃĐsastreux sur le spectre de sortie et il nâ??est guÃre de moyens à mettre en Å?uvre pour sâ??en affranchir. La seule solution est de gÃĐnÃĐrer des frÃĐquences contenues dans la tableâ?.Ceci peut paraÃŪtre farfelu mais en on est bien proche de la rÃĐalitÃĐ quand les DDS sont utilisÃĐs dans les GSM ou autres ÃĐquipements fonctionnant sur une dizaine, voire une centaine de frÃĐquences connues par avance. Dans lâ??utilisation dâ??un DDS ÂŦ en continu Âŧ, il est inÃĐvitable quâ??à de nombreux moments on sera dans une configuration de troncature. Je lâ??ai prÃĐcÃĐdemment montrÃĐ en comparant des spectres sÃĐparÃĐs de quelques centaines de hertz dont lâ??un est tout à fait convenable et lâ??autre trÃs polluÃĐ. 2.3. Bruit de phase : Le bruit de phase est liÃĐ a de nombreux facteurs, on citera : - puretÃĐ spectrale de l'oscillateur d'horloge - rapport frÃĐquence de sortie/ frÃĐquence d'horloge - rÃĐsolution du DAC - dÃĐcouplage des alimentations digitales et analogiques. Les feuilles de spÃĐcifications des DDS AD9850 et AD9852 en ce qui concerne le bruit de phase permettent seulement de comparer les deux DDS gÃĐnÃĐrant un signal à 5 MHz. Les frÃĐquences d'horloge sont maximales (125 pour AD9850 ET 300 MHz pour AD9852). Pour ce dernier, une seconde courbe tient compte de la mise en route du multiplicateur (X 10). Le tableau ci-aprÃs prÃĐsente la synthÃse des rÃĐsultats * : F out = 5MHz 100Hz 1kHz 10kHz 100kHz AD9850 (125MHz CK) -107dBc -134dBc -147dBc -152dBc AD9852 (300 MHz CK) -148dBc -158dBc -160dBc -160dBc AD9852 multi X10 -142dBc -148dBc -138dBc -135dBc - dBc : Niveau du bruit par rapport à la porteuse. * Les valeurs du tableau sont extraits de la lecture des courbes et son naturellement imprÃĐcises. De plus, le bruit propre de l'oscillateur n'est pas renseignÃĐ. On se rend rapidement compte à l'examen de ses rÃĐsultats que des deux DDS, l'AD9852 avec une horloge de 300 MHz directe est trÃs supÃĐrieur à l'AD9852. Avec le multiplicateur en fonction (X10), il le reste jusqu'à 1kHz, au delà , il est battu par l'AD9850. Les rÃĐsultats avec un facteur de multiplication moindre (4 par exemple) ne sont pas communiquÃĐs. 3. MOYENS DE CONTOURNEMENT Dans un rÃĐcepteur oÃđ un DDS est directement utilisÃĐ comme oscillateur local, la prÃĐsence de ces raies parasites, mÊme de faible amplitude, crÃĐe de multiples mÃĐlanges impossible à supprimer et entraÃŪnant une multitude ÂŦ dâ??oiseaux Âŧ pour les pires cas. Les solutions de contournement ne sont pas dâ??une trÃs grande difficultÃĐ ni parfaites et la plus connue est lâ??association dâ??un DDS avec un PLL. Cette combinaison permet de faire fonctionner le DDS à frÃĐquence basse (2 à 3 MHz) ce qui permet de se situer trÃs loin de la frÃĐquence dâ??horloge et de pouvoir filtrer ÃĐnergiquement et de confier à un ou plusieurs VCO la gÃĐnÃĐration proprement dite de la frÃĐquence utile. Les VCO sont contrÃlÃĐs par le PLL, qui reçoit en signal de rÃĐfÃĐrence, la sortie du DDS. Cette solution requiert un nombre important dâ??ÃĐtages car il est nÃĐcessaire de diviser la frÃĐquence de sortie des VCO par une valeur permettant de rabaisser fortement la frÃĐquence du DDS (16 ou 32 ont ÃĐtÃĐ essayÃĐs avec succÃs). Cette division est gÃĐnÃĐralement confiÃĐe à des diviseurs TTL rapide qui nÃĐcessitent quelques volts en entrÃĐe pour fonctionner, dâ??oÃđ amplificateurs à mettre en ouvre. Par ailleurs, un PLL est nÃĐcessaire ainsi que le VCO. Pour la rÃĐalisation de lâ??oscillateur local dâ??un transceiver dÃĐcamÃĐtrique prÃĐsentant de bonnes performances, on se rend compte rapidement quâ??un seul VCO ne saurait couvrir la totalitÃĐ des bandes amateurs car lâ??excursion est trop ÃĐlevÃĐe. Tout dÃĐpend bien ÃĐvidemment du choix de la 1Ãre FI et plus sa frÃĐquence sera ÃĐlevÃĐe, moins lâ??excursion relative (Delta F/F) sera importante. Avec une FI de 36 ou 48 MHz, 4 VCO sont nÃĐcessaires pour couvrir les bandes de 1.8 à 50 MHz, le trois premiers VCO se chargeant de 1.8 à 30 et le dernier exclusivement de la bande 50 MHz. Avec un seul changement de frÃĐquence et une FI de 4.915 MHz, plus de trois VCO seront nÃĐcessairesâ?.On arrive gÃĐnÃĐralement à un VCO par bandeâ?Autant dire que cela devient complexe tant au point de vue des VCO eux-mÊmes que des commutations nÃĐcessaires pour les mettre en Å?uvre au bon moment. Jâ??ai expÃĐrimentÃĐ tous ces montages et il est clair que lâ??amÃĐlioration est substantielle entre un DDS utilisÃĐ en direct et un DDS/VCO. MalgrÃĐ tout, lâ??AD9850 qui a ÃĐtÃĐ et reste encore le DDS le plus utilisÃĐ dans le monde amateur atteint rapidement ses limites pour lâ??ensemble des raisons ÃĐvoquÃĐes ci-dessus. Le DDS AD9851 peut sembler un peu plus prometteur car sa frÃĐquence limite dâ??horloge est de 180 MHz. De plus, il possÃde en interne un multiplicateur qui permet lâ??utilisation dâ??un oscillateur de frÃĐquence infÃĐrieur. En rÃĐalitÃĐ, si lâ??on souhaite un signal sans trop de bruit de phase, le multiplicateur est à prohiber et un oscillateur à 180 MHz est nÃĐcessaire. 4. LE GRAND SAUTâ? Lâ??insatisfaction relative obtenue avec les DDS AD9835, AD9850 et AD9851 mâ??ont fait rechercher un autre type plus performant. Ce DDS existait depuis dÃĐjà quelques annÃĐes mais jâ??avais toujours renoncÃĐ Ã le mettre en Å?uvre de par la difficultÃĐ quâ??il inspire lorsquâ??on lit sa DATA sheet. Pensez donc : Les moins : - BoÃŪtier LQFP de 80 pattesâ?. - Alimentation 3.3V - Codage sur 48 bits (rÃĐsolution < 1ÂĩHz) - Programmation complexe due aux trÃs nombreuses fonctions - Forte consommation - ProblÃmes thermiques - Fils de commande plus nombreux Les plus : - FrÃĐquence horloge 200 ou 300 MHz selon le boÃŪtier (on y reviendra) - DAC 12 bits (extra) - Amplitude de sortie ajustable - Multiplicateur dâ??horloge de 4 à 20 sans trou La tentation ÃĐtait quand mÊme grandeâ?Le soudage du composant qui avait ÃĐtÃĐ le principal frein avait progressivement disparu par les nombreuses poses et dÃĐposes des AD9850. Jâ??avais acquis une technique qui me semblait fiable et je ne voyais pas pourquoi 80 pattes seraient plus difficiles à souder que les 28 de lâ??AD9850 sachant par ailleurs que l'ÃĐcartement entre pattes ÃĐtait le mÊme. Une fois mis en place avec les rÃĐgulateurs 3.3V, jâ??arriverai bien à lui parlerâ? ! Il ne restait plus quâ??à demander deux ÃĐchantillons à Analog Device, ce qui fut fait. 4.1. LA LITTERATURE : La data sheet : La littÃĐrature de base est la ÂŦ data sheet Âŧ dâ??Analog Device. Il faut reconnaÃŪtre â?? et je ne suis pas le seul â?? que ce nâ??est pas un modÃle du genre et elle tranche singuliÃrement avec celle de lâ??AD9850 par exemple. Les 43 pages quâ??elle comportent ne sâ??assimilent pas en une soirÃĐe, loin sâ??en faut : il faut lire et relire, sachant que ce DDS a dâ??ÃĐnormes possibilitÃĐs : - commande parallÃle ou sÃĐrie - modulation phase, frÃĐquence, QPSK, BPSK, FM, FM chirpâ?. - commande dâ??amplitude - mise ON ou OFF de certain circuit interne - multiplicateur dâ??horloge - â?.. Le WEB : Lorsquâ??on recherche ÂŦ AD9852 Âŧ ou ÂŦ AD9854 Âŧ (lâ??AD9854 est quasi similaire à lâ??AD9852) sur le web, on trouve des chosesâ?.. On trouve surtout nombre dâ??expÃĐrimentations rÃĐalisÃĐes à partir de la carte dâ??essai Analog Device de lâ??AD9852 ou alors des AD9852 montÃĐs sur circuit mais commandÃĐs par un PC. Ce nâ??ÃĐtait pas vraiment ce que je recherchais, sachant que je disposais dâ??ores et dÃĐjà dâ??un PIC Microchip 16F877 qui commandait deux AD9850 et que je voulais utiliser car il pilotait une autre carte contenant la partie ÃĐmission/rÃĐception dâ??un transceiver, un jeu de filtres, lâ??afficheur LCD et lâ??encodeur optique de changement de frÃĐquence. Il fallait donc y aller sans filetâ?. 4.2. LE GENERATEUR : Une carte de 13X18 cm est utilisÃĐe pour le gÃĐnÃĐrateur. Elle supporte l'alimentation et le PIC 16F877 qui permettra la commande du DDS via une interface de commande qui permet dâ??abaisser les signaux de niveau 5V issus du PIC à la logique 3.3V requise par le DDS. Ceci ÃĐtant impÃĐratif sous peine de destruction du DDS. Le signal d'horloge est fourni par un oscillateur TTL intÃĐgrÃĐ de 40 MHz. J'ai ÃĐgalement prÃĐvu en option, un second oscillateur utilisant un DDS AD9835 afin de ne pas redessiner la carte si le besoin s'en faisait sentir. Ce second DDS est commandable par le PIC sans modification et utilise l'horloge 40 MHz de l'AD9852. 4.2.1. CONFIGURATION MATERIELLE : Pour notre application point ne sera besoin de modulation, seule la gÃĐnÃĐration d'un signal pur nous intÃĐresse. C'est le mode le plus simple (!) "single tone". Par ailleurs seule la commande en mode sÃĐrie a ÃĐtÃĐ expÃĐrimentÃĐe. La raison principale est le nombre rÃĐduit de fil nÃĐcessaires, ce qui minimise la consommation des ports du PIC. La configuration matÃĐrielle se dÃĐcline alors ainsi : - Masse digitale : Pins 1, 2, 3, 4, 5, 6, 7, 8, 11, 12, 14, 15, 16, 26, 27, 28, 64, 70, 72, 75, 76, 77, 78 (23 pins) - Masse analogique : Pins 33, 34, 39, 40, 41, 45, 46, 47, 53, 59, 62, 66, 67 (13 pins) Remarque : si l'on n'est pas trop regardant sur la puretÃĐ spectrale, on pourra utiliser une masse commune pour l'ensemble de ces 34 pins. J'avoue pour avoir expÃĐrimentÃĐe les deux versions que la diffÃĐrence est peu visible. - +3.3V digital Pins 9, 10, 23, 24, 25, 73, 74, 79, 80 (9 pins) - +3.3V analogique Pins 31, 32, 37, 38, 44, 50, 54, 60, 65 (9 pins) MÊme remarque que pour les masses, il est possible de n'utiliser qu'une seule alimentation et relier les 17 pins au +3.3V - Non connectÃĐe : Pins 13, 18, 20, 29, 35, 36, 42, 43, 57, 58, 63 restent en l'air (11 pins). Voici dÃĐjà 65 pins de casÃĐesâ?.! - Sorties : Pins 48 essentiellement, ou pin 52 car les signaux sont identiques. Ces deux sorties sont chargÃĐes par des rÃĐsistances de 50 ohms (56 en rÃĐalitÃĐ). Si on utilise un AD9854, ces deux sorties sont capables de fournir des signaux dÃĐphasÃĐs de 90°. Avis aux amateurs de phasingâ? Les pin DAC out Iout1 (48) et Iout2 (52) sont simplement chargÃĐes par des rÃĐsistances de 56 ohms et inutilisÃĐes dans cette application. - Comparateur : L'AD9852 dispose d'un comparateur interne rapide qui permet à partir du signal de sortie (ou de tout autre signal d'amplitude # 0dBm) de gÃĐnÃĐrer un signal carrÃĐ d'amplitude 10dBm sur 50 ohms ou 3.3V hors charge. Ceci est particuliÃrement utile pour l'attaque d'un diviseur de PLL par exemple. Les deux entrÃĐes (VINN et VINP - inverseuse et non inverseuse) sont respectivement les pins 43 et 42. La sortie (VOUT) est la pin 36. Ces trois pins ne sont pas utilisÃĐes dans notre application (non connectÃĐes). - DAC RSET pin 56 : Une simple rÃĐsistance entre cette pin et la masse dÃĐfinie l'amplitude maximale des signaux issus du DAC en fonction de la rÃĐsistance de charge car c'est une sortie en courant. Les valeurs normales s'ÃĐtendent de 2k à 8kohms. La valeur utilisÃĐes sur la carte d'essai est de 3.9k. Plus la rÃĐsistance est faible, plus grande est l'amplitude de sortie. Par contre la distorsion augmente. - DAC BP (dÃĐcouplage du DAC) pin 55 Un simple condensateur de 10nF entre cette pin et le +3.3 analogique amÃĐliore la distorsion harmonique et lÃĐgÃrement la puretÃĐ spectrale. On peut ÃĐventuellement s'en passer mais ça ne coÃŧte pas grand chose de la monterâ? - PLL FILTER pin 61 Un rÃĐseau sÃĐrie 100nF /1.3k connectÃĐ entre cette pin et le +3.3V analogique assure la compensation du PLL de la partie multiplicateur d'horloge. Si ce multiplicateur n'est pas utilisÃĐ, il n'est pas nÃĐcessaire de monter ce circuit. Pour essai, il a ÃĐtÃĐ installÃĐ sur la carte. - S/P select pin 70 : L'ÃĐtat de cette pin dÃĐfinie le mode de communication vers le DDS : niveau bas pour liaison sÃĐrie, haut pour liaison parallÃle. Le mode sÃĐrie est retenue ici. - Master RESET pin 71 : Comme indiquÃĐ dans la data sheet "le master reset" est essentiel pour un dÃĐmarrage du DDS à la mise sous tension. La plupart des applications recensÃĐes utilisent une sortie spÃĐcifique du PIC ou du PC pour commander cette entrÃĐe. J'ai tentÃĐ d'ÃĐconomiser une sortie du PIC en utilisant un circuit RC pour maintenir le +3.3V quelques millisecondes sur l'entrÃĐe Master Reset. Cette solution ne s'est pas avÃĐrÃĐe suffisammment fiable pour la conserver (le dÃĐmarrage ne s'effectuait pas systÃĐmatiquement). Aussi, le Master reset a ÃĐtÃĐ confiÃĐ au logiciel et permet dorÃĐnavant un dÃĐmarrage sans dificultÃĐ. - SDIO pin 19 : Il s'agit de l'entrÃĐe du message de programmation (DATA) à destination des registres du DDS. Les donnÃĐes sont gÃĐnÃĐrÃĐes par le bus SPI du PIC. C'est la pin "DATA" de l'AD9850. - SCLK pin 21 : L'horloge de cadencement des donnÃĐes est appliquÃĐes à cette entrÃĐe. La frÃĐquence maximale est de 20 MHz. Il s'agit de l'ÃĐquivalence de la pin W_CLK de l'AD9850. - CSB Chip select pin 22 : Cette patte permet de sÃĐlectionner ou non le DDS. Ceci est particuliÃrement utile lorsque le bus SPI est utilisÃĐ pour commander d'autre pÃĐriphÃĐrique (afficheur LCD, registresâ?) Un niveau bas active l'AD9852. Pas d'ÃĐquivalence pour l'AD9850. - IO RESET pin 17 : Cette pin permet de rÃĐinitialiser la communication sÃĐrie si la programmation n'a pas ÃĐtÃĐ conforme au protocole imposÃĐ. Par prudence, cette pin sera utilisÃĐe à la fin de chaque envoi de donnÃĐes. - IO/ Update clock : Cette pin est systÃĐmatiquement utilisÃĐes dans les applications rencontrÃĐes. Sa fonction est double car bidirectionnelle. En entrÃĐe, un niveau haut transfert les donnÃĐes contenues dans le buffer d'entrÃĐe vers les registres de programmation. En sortie, un front haut indique que la frÃĐquence gÃĐnÃĐrÃĐe a ÃĐtÃĐ modifiÃĐe. En fait, on peut se passer d'utiliser cette pin en laissant le DDS gÃĐrer lui-mÊme le temps nÃĐcessaire pour mettre à jour les donnÃĐes reçues. Bien que ce temps soit programmable par l'utilisateur, la valeur par dÃĐfaut (0x40) s'est avÃĐrÃĐe tout à fait adaptÃĐe. - REFCLCK pin 69 C'est l'entrÃĐe de l'horloge principale qui fixera les valeurs de frÃĐquence de sortie en fonction de la programmation. A noter qu'une possibilitÃĐ d'entrer en diffÃĐrentiel est proposÃĐe. Si elle n'est pas utilisÃĐe, la pin 64 (DIFF CLK ENABLE) sera mise à la masse. En mode normal, la tension requise est de 400 mV c/c (carrÃĐ ou sinus) centrÃĐe sur 1.6V (3.3V/2). 4.2.2. ASPECTS THERMIQUES : Ils sont importants et doivent Être pris d'emblÃĐe en considÃĐration. Il faut savoir en effet que diffÃĐrents paramÃtres influent sur la consommation du circuit et par la mÊme sur la puissance à dissiper. Nous retiendrons trois de ces paramÃtres : - La tension d'alimentation : Avec une tension d'alimentation aussi rÃĐduite que 3.3V, les variations de cette derniÃre influent grandement que la puissance consommÃĐes (P=UI). La plage de tensions acceptables par l'AD9852 s'ÃĐtend de 3.135V à 3.465V. On s'efforcera de rester autour de 3.3V, voire lÃĐgÃrement en dessous. - La frÃĐquence de l'horloge : La consommation croÃŪt de façon linÃĐaire avec la frÃĐquence de l'horloge. Les mesures rÃĐalisÃĐes montrent une consommation de l'ordre de 100 mA à 100 MHz, 400 mA à 200 MHz et prÃs de 600 mA à 300 MHz. - Le filtre inverse : Le filtre inverse est un ÃĐlÃĐment du DDS qui permet de maintenir l'amplitude du niveau de sortie constant quelque soit la frÃĐquence. Cet niveau s'attÃĐnuant naturellement lorsque la frÃĐquence augmente. La consommation de ce circuit est trÃs importante et varie avec la frÃĐquence de l'horloge de rÃĐfÃĐrence. A 200 MHz, il faut compter 300 mA, plus de 400mA à 300 MHz. On s'efforcera donc de ne pas utiliser cette fonctionnalitÃĐ, le rÃĐglage de l'amplitude pouvant Être rÃĐalisÃĐ par programmation. L'AD9852 existe sous deux boÃŪtiers diffÃĐrents le boÃŪtier AST (tout plastique) et le boÃŪtier ASQ qui est muni à sa partie infÃĐrieure d'une semelle mÃĐtallique destinÃĐe à l'ÃĐvacuation des calories. Les dissipations respectives de ces deux boÃŪtiers sont 1.7W et 4.1W. La rÃgle recommandÃĐe par Analog Device est de limiter l'utilisation du boÃŪtier AST à 200MHz, seul le modÃle ASQ permettant de monter à 300 MHz moyennant certaines prÃĐcautions. On verra plus loin que cette rÃgle peut Être transgressÃĐe moyennant quelques amÃĐnagements. 4.2.3. INTERFACE DE COMMANDE : Comme mentionnÃĐ ci dessus, la commande du DDS est rÃĐalisÃĐe à partir d'un PIC Microchip 16F877, un 16F876 moins encombrant est certainement utilisable moyennant une redistribution des E/S L'adaptation des niveaux 5V/3.3V est effectuÃĐe simplement par un rÃĐseau de diodes et rÃĐsistances. L'utilisation d'un circuit intÃĐgrÃĐ d'interface n'a pas ÃĐtÃĐ tentÃĐ. Un afficheur LCD 2X16 caractÃres permet la visualisation de la frÃĐquence courante et du pas d'incrÃĐmentation. Un clavier type calculatrice permet l'accÃs aux diffÃĐrentes fonctions ci-aprÃs : - IncrÃĐmentation et dÃĐcrÃĐmentation de la frÃĐquence de sortie - IncrÃĐmentation et dÃĐcrÃĐmentation du pas (10HZ, 100Hz, 1kHz, 10kHz et 100 kHz) - PrÃĐpositionnement sur frÃĐquences favorites. Le logiciel de base permet l'utilisation du DDS AD9852 en gÃĐnÃĐrateur BF/HF, de quelques Hz jusqu'à une centaine de MHz * * La frÃĐquence de coupure du filtre de sortie est de 120 MHz, ce qui permet de monter la frÃĐquence d'horloge à 300 MHz. 5. REALISATION DU GENERATEUR : 5.1. SCHEMAS Le logiciel de CAO utilisÃĐ est ISIS de Proteus, je tiens à disposition les fichiers correspondants pour les intÃĐressÃĐs. Les schÃĐmas comprennent 3 parties physiquement distinctes : -DDS -PIC -Afficheur LCD 5.1.2. Partie DDS : Le schÃĐma de la partie DDS est conforme à ce qui a ÃĐtÃĐ dÃĐcrit prÃĐcÃĐdemment, par contre la simplicitÃĐ a fait regrouper respectivement les alimentations et les masses analogiques et digitales. Un oscillateur 40 MHz rÃĐcupÃĐrÃĐ sur une carte de PC (autres valeurs possibles) est utilisÃĐ pour la gÃĐnÃĐration du signal de l'horloge de rÃĐfÃĐrence. Bien que sa tension nominale de fonctionnement soit de 5V, il fonctionne parfaitement sous 3.3V et est donc compatible avec le DDS. La fonction multiplicateur du DDS sera utilisÃĐe pour obtenir une frÃĐquence finale de 200 MHz, voire plus si l'on consent de munir le DDS d'un radiateur contre sa face supÃĐrieure. Ce dernier sera fixÃĐ par 4 vis aux emplacement prÃĐvus sur le circuit imprimÃĐ. Les essais ont montrÃĐs qu'il est possible d'atteindre sans difficultÃĐ 400 MHz (multiplication par 10), la frÃĐquence limite ÃĐtant au voisinage de 430/440MHz. ATTENTION : la puissance dissipÃĐe devient importante et le circuit chauffe trÃs rapidement. Le fonctionnement au delà de 200 MHz sans radiateur avec un boÃŪtier AST n'est pas garanti. Le circuit de sortie est muni d'un filtre elliptique à deux cellules coupant à 120 MHz. En fonction de l'utilisation, cet filtre pourra bien entendu Être recalculÃĐ pour tout autre frÃĐquence. L'amplificateur de sortie utilise un MSA 2643 qui à l'avantage de fonctionner sous 5V par rapport au MAV. Il procure un gain d'une quinzaine de dB et la puissance de sortie avoisine +10dBm. Le courant est ÃĐtabli à 33mA par R11 150 ohms. On pourra rÃĐduire cette valeur si l'on souhaite un peu plus de gain et de puissance en sortie, ne pas descendre toutefois en deçà de 82 ohms (60mA). 5.1.2. Partie PIC : Le circuit du PIC 16F877-20 est minimal. Deux connecteurs sont requis pour interfacer l'afficheur LCD et le clavier. L'horloge est obtenu à partir d'un quartz 20 MHz. Un 4MHz avec un PIC 16F877-04 convient ÃĐgalement (les deux PIC sont au mÊme prix chez certains distributeurs). On aurait ÃĐgalement pu mettre en Å?uvre un 16F876 moins encombrant mais le 16F877 ayant dÃĐjà ÃĐtÃĐ utilisÃĐ, j'ai prÃĐfÃĐrÃĐ ne rien changerâ? Un connecteur SIL 4 broches permet la programmation in-situ du PIC moyennant le programmeur appropriÃĐ. 5.1.3. Alimentation : Elle est des plus simple. Deux rÃĐgulateurs ont ÃĐtÃĐ prÃĐvus pour les tensions de +5V et +3.3V. On prÃĐfÃĐrera les versions faible chute de tension "low-drop". Le montage sera alimentÃĐ avec une source de tension continue de 7 à 10V capable de fournir 600 mA. Suivant la tension disponible, un radiateur pourra s'avÃĐrer nÃĐcessaire sur le rÃĐgulateur 5V. 5.1.4. Afficheur LCD : L'afficheur est du type 2 lignes de 16 caractÃre rÃĐtro-ÃĐclairÃĐ que l'on trouve maintenant partout à un prix trÃs abordable. La commande est assurÃĐe en mode sÃĐrie par le bus SPI du PIC et un registre sÃĐrie/parallÃle (74HC164) montÃĐ sur une petite carte solidaire de l'afficheur. L'ensemble est reliÃĐ Ã la carte PIC/DDS par un connecteur HE 10 broches. 5.1.5. Clavier : Le clavier est un modÃle alphanumÃĐrique à 16 touches, bien plus que nÃĐcessaire, mais c'est ce que j'avais sous la main. Une petit circuit imprimÃĐ fixÃĐ Ã l'arriÃre du clavier et muni d'un connecteur HE 10 broches permet sa liaison avec la carte PIC/DDS. 5.2. Circuit imprimÃĐ : 5.2.1. RÃĐalisation du circuit imprimÃĐ carte PIC/DDS Le logiciel de CAO utilisÃĐ est ARES de Proteus, je tiens à disposition les fichiers correspondants pour les intÃĐressÃĐs. Le dessin du circuit imprimÃĐ est localisÃĐ sur le site version anglaise de l'article (pour le poment) et permet sa rÃĐalisation en simple face. La rÃĐalisation correcte et minutieuse du calque sera de premiÃre importance car les pistes sont relativement fines. On veillera particuliÃrement au contraste afin d'obtenir une insolation franche de l'ÃĐpoxy prÃĐsensibilisÃĐ et un dÃĐveloppement net de l'ensemble des pistes. La surface de cuivre à dissoudre a ÃĐtÃĐ rÃĐduite au minimum afin de permettre une attaque rapide et complÃte sans devoir laisser le circuit trop longtemps dans le perchlorure de fer pour dissoudre entiÃrement de grandes zones de cuivre. Ceci ÃĐtant prÃĐjudiciable aux pistes fine qui se trouvent alors "sur attaquÃĐes" et qui peuvent alors prÃĐsenter des micro coupures toujours difficiles à dÃĐceler. Une fois le circuit dÃĐveloppÃĐ, on procÃĐdera au perçage des 143 trous puis à l'ÃĐlimination à l'alcool et à la laine d'acier la couche sensible et les bavures. L'ÃĐtamage à froid est recommandÃĐ. Pour plus de dÃĐtails, voir RÃĐalisation des circuits imprimÃĐs sur ce mÊme site. 5.2.2. Mise en place des composants (100 ÃĐlÃĐments) Avant toute mise en place des composants, on implantera les 18 straps permettant de s'affranchir du double face. Attention à celui qui est prÃs du PIC, il est proche des pattes. Les CMS seront ensuite mis en place, puis le reste des composants exceptÃĐ le DDS et le PIC. A ce stade, il sera nÃĐcessaire de vÃĐrifier le bon fonctionnement des rÃĐgulateurs en mesurant les tensions de sortie : +5V sur U5 et +3.3V sur U4. Toute tension diffÃĐrente est signe d'une oscillation qui, avec les valeurs utilisÃĐes ne devrait pas survenir. 5.2.3. Mise en place du DDS : C'est la principale difficultÃĐ Le tracÃĐ des pistes des circuit imprimÃĐ se doit d'Être impeccable, c'est un prÃĐalable indispensable à la rÃĐussite de l'opÃĐration. La procÃĐdure à suivre est la suivante : On commencera par identifier la patte 1 du composants repÃĐrÃĐe par un point placÃĐ sur la face supÃĐrieur du boÃŪtier à l'un des angle. - Le boÃŪtier sera orientÃĐ afin que le point mentionnÃĐ soit approximativement dans la direction de la bissectrice de l'angle formÃĐ par les rÃĐgulateurs et le boÃŪtier de l'oscillateur d'horloge (DIL). - Placer le boÃŪtier en face de chaque piste afin d'obtenir le meilleure recouvrement possible des 80 pattes avec les 80 pistes puis maintenir le DDS avec un poids posÃĐ sur sa face supÃĐrieure (bloc de mÃĐtal, outilâ?) - VÃĐrifier que rien n'a bougÃĐ - Souder le composants aux quatre angles - Enlever le poids - Le fer à souder ÃĐtant suffisamment chaud (350°C), noyer les 20 pattes d'un mÊme cÃtÃĐ avec la soudure sans lÃĐsiner sur la soudure. (voir photo ci-contre). A ce moment, les 20 pattes ne doivent plus Être quasiment visibles et remplacÃĐes par un cordon de soudure uniforme. - Laisser refroidir quelques instants (30 secondes). - RÃĐpÃĐter la mÊme opÃĐration pour les 3 cÃtÃĐs restants. La "chose" doit alors se prÃĐsenter comme ci-dessousâ?!

(cliquer pour agrandir) - A l'aide de la tresse à dessouder, en conservant la mÊme tempÃĐrature du fer, absorber la soudure dÃĐposÃĐe afin de dÃĐgager les 20 premiÃres pattes. Cette opÃĐration doit se faire assez rapidement mais sans hÃĒte, c'est la plus dÃĐlicate car aucun reste de soudure ne doit venir cout-circuiter deux pattes adjacentes. - RÃĐpÃĐter la mÊme opÃĐration sur les trois autres cÃtÃĐs. - A l'issue de ces opÃĐrations, le circuit doit apparaÃŪtre propre sans reliquat indÃĐsirable de soudure :

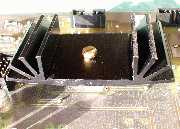

Si ce n'est pas le cas, renouveler l'opÃĐration. C'est finiâ?.! 5.2.4. VÃĐrification avant mise sous tension : Cette opÃĐration est indispensable mÊme si l'on est sÃŧr de son travail. - prendre un ohmÃtre (calibre 200 ohms ou moins) et le schÃĐma du circuit. tester la continuitÃĐ de chaque pin du DDS avec les composants associÃĐs, les pin du PIC, l'alimentation 3.3V et la masse. tester tous les court-circuits potentiels entre pattes 5.2.5. Mise en place du radiateur sur l'AD9852 AST : Si la frÃĐquence d'horloge reste infÃĐrieure à 200 MHz, cette opÃĐration n'est pas indispensable, quoique conseillÃĐe par sÃĐcuritÃĐ. Le radiateur pourra se rÃĐduire à une simple plaque d'aluminium de 33X56 mm environ, ou mieux de cuivre mise en contact avec la face supÃĐrieur du DDS via une lÃĐgÃre couche de graisse thermique. Un modÃle pour T0220 convient ÃĐgalement. Sa fixation sera assurÃĐe par quatre vis dont les emplacement sont repÃĐrÃĐs sur le circuit imprimÃĐ. 5.2.6. Mise en place du radiateur sur l'AD9852 ASQ : Cette opÃĐration n'est nÃĐcessaire qui si on souhaite fonctionner à des frÃĐquences d'horloge de 300 MHz et plus. Le modÃle ASQ possÃde donc une semelle mÃĐtallique sur sa face infÃĐrieure qui permet un meilleur ÃĐchange que le boÃŪtier tout plastique de l'AST. Analog Device recommande de souder cette partie mÃĐtallique sur le circuit imprimÃĐ. Cette opÃĐration à mon avis sort du domaine de l'amateur, sachant que simultanÃĐment, il est nÃĐcessaire de positionner le composant trÃs prÃĐcisÃĐment. Pour contourner ce problÃme j'ai imaginÃĐ de percer une ouverture dans le circuit imprimÃĐ situÃĐ sous le DDS, au regard de la semelle mÃĐtallique, un trou carrÃĐ de 10mm de cÃtÃĐ a ÃĐtÃĐ rÃĐalisÃĐ, attention au circuit imprimÃĐ pendant le perçageâ?.!

Une fois le DDS soudÃĐ sur le circuit (voir plus haut), il laisse donc apparaÃŪtre sa semelle mÃĐtallique. Un cube de cuivre de 10mm d'arÊte est alors usinÃĐ (à la main) puis percÃĐ et tarauder borgne sur une des faces. On veillera à ce que deux faces opposÃĐes du cube soient parfaitement planes et de prÃĐfÃĐrence parallÃles.

Le cuivre est ensuite plaquÃĐ contre la semelle du DDS (face plane) en interposant une trÃs lÃĐgÃre couche de graisse thermique. La face taraudÃĐe doit se trouvÃĐe visible et parallÃle au circuit imprimÃĐ. Le cube de cuivre est alors collÃĐ Ã la rÃĐsine ÃĐpoxy sur le circuit imprimÃĐ tout en maintenant une pression suffisante contre le DDS. AprÃs sÃĐchage complet, un radiateur est alors fixÃĐ sur le cube à l'aide d'une vis de 4mm.

Les essais rÃĐalisÃĐs jusqu'à 430 MHz pendant plusieurs heures montrent que le dispositif est particuliÃrement efficace : le radiateur chauffe sensiblement mais maintient une tempÃĐrature plus qu'acceptable pour le DDS. Rappelons qu'un telle frÃĐquence d'horloge permet la gÃĐnÃĐration d'un signal de sortie à 175 MHzâ?. * Un trou rond de 10mm de diamÃtre plus facile à faire remplit tout aussi bien sinon mieux la fonction. Dans l'hypothÃse d'une catastrophe, d'un claquage du DDS ou autre, on s'inspirera de la photo ci-contre pour dÃĐposer le circuit sans rendre le CI inutilisable..

Les pattes du DDS seront coupÃĐes à raz du boÃŪtier avec une lame neuve de cutter. Les pattes et la soudure restant seront enlevÃĐes à la tresse à souder SANS APPUYER sur le circuit imprimÃĐ sous peine de dÃĐcoller les pistes.... La photo montre la version avec radiateur : on aperçoit la face du cube de cuivre en contact avec la semelle du DDS (version ASQ). 5.2.7. Circuit imprimÃĐ afficheur LCD : Rien à voir avec l'exercice prÃĐcÃĐdentâ?la carte de l'afficheur est des plus simple et ne pose aucune difficultÃĐ. 5.2.8. Carte clavier : Aucune difficultÃĐ 6. LE LOGICIEL : Les notions de base relatives aux PIC ont largement ÃĐtÃĐ prÃĐsentÃĐes dans les articles prÃĐcÃĐdents et la littÃĐrature relative à ces PIC, au langage et à la programmation est abondante. Je me contenterai d'expliciter les diffÃĐrentes opÃĐrations permettant d'initialiser le DDS AD9852 puis de gÃĐnÃĐrer la frÃĐquence souhaitÃĐe. Le DDS AD9852 possÃde 12 registres de commande contenant chacun un ou plusieurs octets (de 1 à 6). Chacun de ces registres permet diverses opÃĐrations telles que la configuration, la gÃĐnÃĐration de la frÃĐquence, de la phase, des diffÃĐrents types de modulationâ?. Dans le mode signal pur (single tone) qui nous intÃĐresse, seulement 2, voire 3 registres seront nÃĐcessaires. La programmation d'un registre nÃĐcessite impÃĐrativement l'ÃĐcriture de l'ensemble des bits de ce registre. Si le registre comporte 28 bits, les 4 octets correspondants devront Être envoyÃĐs au DDS par le PIC. 6.1. Initialisation du DDS AD9852 PrÃĐalablement à la gÃĐnÃĐration de frÃĐquence, il est nÃĐcessaire d'intialiser le DDS, c'est à dire de le configurer dans le mode souhaitÃĐ. Plusieurs opÃĐrations sont nÃĐcessaires et indispensables, d'autres facultatives : 6.1.1. RESET : Je le signale pour mÃĐmoire car comme indiquÃĐ prÃĐcÃĐdemment, le RESET est rÃĐalisÃĐ par le logiciel une fois que les alimentations sont montÃĐes car l'activation du RESET suppose que le DDS reçoive les signaux de l'horloge de rÃĐfÃĐrence (40 MHz) pour s'initialiser. 6.1.2. Configuration du bus SPI du PIC : Le bus SPI qui permet la gÃĐnÃĐration de l'horloge de travail et des donnÃĐes a du et doit Être configurÃĐ spÃĐcialement avant tout envoi de commande vers le DDS. Je ne m'explique pas totalement la raison, toujours est-il que c'est nÃĐcessaireâ?.Le mode destinÃĐ au DDS diffÃre uniquement du mode utilisÃĐ pour les autres pÃĐriphÃĐriques par la vitesse d'envoi des donnÃĐes. Il est nÃĐcessaire de descendre à Fhorloge PIC/16, soit 1.25 MHz pour avoir un fonctionnement satisfaisant. Ceci est contraire à la spÃĐcification qui autorise 10 MHz. Le registre correspondant du PIC est SSPCON qui sera chargÃĐ Ã 0x31. A l'issue de l'envoi des commandes vers le DDS, SSPCON sera chargÃĐ Ã 0x30 (F/4) 6.1.3. SÃĐlection du DDS par le chip select : On fait descendre la pin 22 à 0 pour sÃĐlectionner le DDS. Tant que cette pin est à 0, le DDS reçoit et accepte les commandes. 6.1.4. Remise à zÃĐro de la communication sÃĐrie On fait montÃĐ puis descendre la pin 17 IO/reset. Ceci permet d'initialiser proprement le dialogue avec le DDS. 6.1.5. Programmation de la configuration du registre de contrÃle : L'adresse du registre de contrÃle en mode sÃĐrie du DDS est 0x07. L'ÃĐcriture dans ce registre requiert l'envoi de l'adresse du registre (0x07) suivi de 4 octets indissociables. SI c'est 4 octets ne sont pas tous envoyÃĐs, une erreur de communication sera gÃĐnÃĐrÃĐe car en rÃĐalitÃĐ le DDS s'attend à recevoir un mot de 32 bits Le registre de contrÃle permet de dÃĐfinir le rÃĐgime de fonctionnement du DDS et entre autres : - la mise ON ou OFF du multiplicateur - le facteur de multiplication (4 à 20 par pas de 1) - la mise ON/OFF du filtre inverse - la mise ON/OFF du comparateur - l'ordre de prise en compte du message de programmation (poids faible ou poids fort en tÊte) - la gÃĐnÃĐration interne ou externe du signal Update Clockâ?.. Cette configuration sera dÃĐfinie en principe une fois pour toute (en ce qui nous concerne), rien n'empÊche toutefois de la modifier à n'importe quel moment si nÃĐcessaire. Dans l'application prÃĐsente, les 32 bits du registre de contrÃle sont ainsi dÃĐfini : On a dÃĐcoupÃĐ les 32 bits en 4 octets car le PIC travaille sur 8 bitsâ? 1er octet : b'00010100' (0x14) Bit 31 : sans effet , valeur =0 Bit 30 : sans effet , valeur =0 Bit 29 : sans effet, valeur = 0 Bit 28 : Comparateur ON/OFF = 1 (OFF) Bit 27 : RÃĐservÃĐ AD, valeur =0 Bit 26 : Control DAC ON/OFF, valeur = 1 (OFF) Bit 25 : DAC ON/OFF, valeur = 0 (ON) Bit 24 : Partie digitale ON/OFF, valeur = 0 (ON) 2Ãme octet : b' 00000101' (0x04) pour un facteur de multiplication de 5 Bit 23 : sans effet, valeur = 0 Bit 22 : PLL Range high, valeur = 0 (si frÃĐquence de rÃĐfÃĐrence multipliÃĐe < 200 MHz, valeur = 1) Bit 21 : PLL ON/OFF, valeur = 0 (PLL ON) Bit 20, 19, 18, 17 et 16 : valeur de multiplication de l'horloge de rÃĐfÃĐrence. La valeur est en clair, codÃĐe en binaire de 4 à 20 sans trou : 4 : 00100 5 : 00101 6 : 00110 7 : 00111 8 : 01000 9 : 01001 10 : 01010 11 : 01011 â?. 20 : 11111 3Ãme octet : b'00000001' (0x01) Bit 15 : Valeur = 0 (non utilisÃĐ en CW) Bit 14 : valeur = 0 (non utilisÃĐ en CW) Bit 13 : Triangle, valeur = 0 (non utilisÃĐe en CW) Bit 12 : sans effet, valeur = 0 Bit 11, 10 et 9 : mode de modulation, valeur = 0 (CW / Single tone) Bit 10 : Update clock interne ou externe, valeur = 1 (interne) 4Ãme octet : b'01000000' ( 0x60) Bit 7 : sans effet, valeur = 0 Bit 6 : filtre inverse ON/OFF, valeur = 1 (OFF) Bit 5 : multiplicateur digital ON valeur = 1 (commande de la tension de sortie) Bit 4 : non utilisÃĐ en CW, valeur = 0 Bit 3 : sans effet, valeur = 0 Bit 2 : sans effet, valeur = 0 Bit 1 : LSB en premier ou non, valeur = 0 (MSB) Bit 0 : SDO active ou non, valeur = 0 (inactive) La sÃĐquence indissociable correspondante est donc 0x07 (adresse du registre) 0x14 (byte 1) 0x04 (byte 2) 0x01 (byte 3) 0x60 (byte 4) C'est tout pour la configurationâ?.! A l'issue de cet envoi, on activera IO/Reset afin d'Être prÊt pour la commande suivante, puis le DDS sera dÃĐsÃĐlectionnÃĐ en appliquant un niveau haut sur la pin 22. 6.2. PROGRAMMATION DE LA FREQUENCE DE SORTIE : Nous arrivons maintenant à l'essentiel car c'est bien l'objectif à atteindre que de gÃĐnÃĐrer un signal de frÃĐquence dÃĐsirÃĐeâ?! Pour gÃĐnÃĐrer une frÃĐquence donnÃĐes le DDS AD9852 nÃĐcessite l'envoi d'un mot de 48 bits, soit 6 octets pour le PIC. On est donc en prÃĐsence d'une diffÃĐrence notable avec les AD935 et AD9850 pour lesquels ont ÃĐtÃĐ dÃĐcrit par le passÃĐ le mÃĐcanisme de calcul. C'est pourquoi je le redÃĐtaille ci-aprÃs: Les 48 bits vont devoir Être ÃĐlaborer automatiquement par le logiciel contenu dans le PIC et pouvoir Être modifiÃĐs à loisir par l'opÃĐrateur afin de pouvoir faire varier cette frÃĐquence. L'intÃĐrÊt de n'avoir qu'une seul frÃĐquence de valeur fixe ÃĐtant plus que limitÃĐâ? 6.2.1. Elaboration des 6 octets (48 bits) : Le mot qu'il va falloir charger dans l'AD9852 est directement fonction de deux paramÃtres : - la frÃĐquence à gÃĐnÃĐrer - la frÃĐquence de l'horloge de rÃĐfÃĐrence (aprÃs multiplication si le multiplicateur est en service) La relation qui unit ces deux paramÃtres est la suivante : Valeur du mot de 48 bits = (FrÃĐquence de sortie X 2 exp 48) / FrÃĐquence horloge de rÃĐfÃĐrence L'opÃĐration mathÃĐmatique correspondante n'est pas triviale avec un calculateur 8 bits (PIC) et c'est une des difficultÃĐs de la programmation. Bien des algorithmes ont ÃĐtÃĐ ÃĐcrits pour rÃĐsoudre cette ÃĐquation, pour ma part j'utilise une solution que je pense inÃĐdite et qui consiste à dÃĐfinir la valeur de chaque octet pour des frÃĐquences entiÃres de 10Hz, 100Hz, 1KHz, 10kHz, 100 kHz, 1MHz et 10 MHz. Ces frÃĐquences entiÃre correspondant aux diffÃĐrents digits de l'afficheur LCD sur lequel sera affichÃĐe la frÃĐquence de sortie. Lorsque l'on fait varier la frÃĐquence, on met d'abord à jour l'affichage du LCD puis on transforme la valeur de chaque caractÃre affichÃĐ en un octet destinÃĐ au DDS. Cette façon de faire à l'avantage d'Être certain que la frÃĐquence affichÃĐe est bien ÃĐgale à la frÃĐquence gÃĐnÃĐrÃĐe. Pour dÃĐterminer une fois pour toute la valeur de chaque octet correspondant aux frÃĐquences entiÃres, une calculette hexadÃĐcimale est suffisante, une macro Excel est ÃĐgalement disponible auprÃs de l'auteur. Exemple : Soit une frÃĐquence d'horloge de rÃĐfÃĐrence de 200 MHz, les valeurs correspondantes sont les suivantes : 200MHz 10Hz 100Hz 1k 10k 100k 1M 10M ACC5 00 00 00 00 00 01 0C ACC4 00 00 00 03 20 47 CC ACC3 00 08 53 46 C4 AE CC ACC2 D6 63 E2 DC 9B 14 CC ACC1 BF 7B D6 5D A5 7A CC ACC0 94 D0 23 63 E3 E1 CC ACC0 à ACC5 sont les 6 octets correspondants, ACC0 ÃĐtant le byte de poids faible, ACC5 celui de poids fort. Pour une frÃĐquence diffÃĐrente d'horloge de rÃĐfÃĐrence, ces valeurs seront à recalculer. La reconstitution de la frÃĐquence 21 263.84 kHz par le programme s'effectuera de la façon suivante : 2(0C CC CC CC CC)+ 1(01 47 AE 14 7A E1)+2(00 20 C4 9B A5 E3)+6(00 03 46 DC 5D 63)+3(00 00 530E2 D6023)+8(00 00 08 63 7B0 D0)+4(00 00 00 D6 BF 94) Soit : ACC5 = 1B ACC4 = 37 ACC3 = BC ACC2 = 2E ACC1 = EF ACC0 = D7 6.2.2. Chargement Ces 6 octets seront chargÃĐs dans le registre frÃĐquence DDS (adresse 0x02) sÃĐquentiellement, poids fort en tÊte. La sÃĐquence correspondante est la suivante : - Configuration SPI - Chip select niveau bas - Octet adresse (0x02) - Octet ACC5 - Octet ACC4 - Octet ACC3 - Octet ACC2 - Octet ACC1 - Octet ACC0 - IO Reset niveau haut - IO Reset niveau bas - Chip select niveau haut - Configuration SPI A l'issue de cette opÃĐration, la frÃĐquence apparaÃŪt en sortie du DDS. Chaque fois que la frÃĐquence est modifiÃĐe, l'afficheur LCD est mis à jour, les octets DDS sont recalculÃĐs et ensuite chargÃĐs. L'ensemble de ces opÃĐrations est lourde pour le PIC et les sous-programmes correspondant ont ÃĐtÃĐ optimisÃĐs afin de permettre plusieurs dizaines de modifications de la frÃĐquence chaque seconde (cas de l'utilisation d'un encodeur optique pour faire varier la frÃĐquence). Par exemple, seuls sont pris en compte les digits de l'afficheur qui ont changÃĐs. 6.3. PROGRAMMATION DU NIVEAU DE SORTIE : Il peut Être intÃĐressant de pouvoir faire varier le niveau de sortie afin d'ÃĐgaliser la rÃĐponse en frÃĐquence du DDS ou encore de n'injecter que ce qui est nÃĐcessaire sans recourir à un attÃĐnuateur. De plus, en restant lÃĐgÃrement en deçà du niveau maximal, la puretÃĐ spectrale est amÃĐliorÃĐe de 11dB*. Cette variation est rÃĐalisÃĐ par un des sous-ensemble du DDS AD9852 appelÃĐ multiplicateur digital. La commande de l'amplitude est ajustable sur 4096 pas et est rÃĐalisÃĐe par l'envoi de 2 octets (12 bits utiles ) à l'adresse 0x08. On ne dÃĐveloppera pas ici la sÃĐquence correspondante qui est identique aux deux prÃĐcÃĐdentes. La variation du niveau de sortie rÃĐalisÃĐe par le programme n'exploite pas les 4096 pas disponible mais se limite à 16 positions offrant chacune une attÃĐnuation de 6dB. * Valeur mentionnÃĐe par AD (page 35 de la data sheet) pour une amplitude de 4032 pas au lieu de 4096 soit 98.4 % de la valeur maximale de sortie. 7. PROGRAMMATION DU PIC : Si l'on dispose d'un programmeur de PIC Microchip, l'auteur est en mesure de fournir le code, sinon je peux fournir le PIC programmÃĐ. 8. ESSAIS : 8.1. Mise sous tension : InsÃĐrer le Pic programmÃĐ dans son support et appliquer une tension continue de 7 à 10V sur les bornes d'alimentation. Si tout ce qui vient d'Être dÃĐcrit à ÃĐtÃĐ rÃĐalisÃĐ correctement il n'y a pas d'obstacle à ce que le systÃme dÃĐmarre du premier coup. Le message " BIENVENU HAM GENE 52" doit apparaÃŪtre sur les deux lignes, suivi immÃĐdiatement de "F6EHJ - HAM GENE 52" . La frÃĐquence de 10 000.00 et le pas de 10H s'affichent ensuite. On peur alors vÃĐrifier la prÃĐsence en sortie du DDS d'un signal de frÃĐquence 10000.00 kHz et de +10 dBm environ d'amplitude. La prÃĐcision de la frÃĐquence gÃĐnÃĐrÃĐe dÃĐpend uniquement de l'oscillateur 40 MHz. Si ce dernier n'oscille pas exactement sur cette frÃĐquence, un ÃĐcart proportionnel sera prÃĐsent en sortie du DDS. 8.2. Variation de la frÃĐquence : Elle s'effectue en pressant sur la touche 3, la frÃĐquence s'incrÃĐmente de la valeur du pas courant, la touche 6 produit l'effet inverse. 8.3. Variation du pas : Elle s'effectue en pressant sur la touche 2, le pas s'incrÃĐmente de 10 Hz à 100 kHz, la touche 5 produit l'effet inverse. 8.4. PrÃĐpositionnement : Une dizaine de frÃĐquences ont ÃĐtÃĐ mises en mÃĐmoire (il s'agit de la frÃĐquence de dÃĐbut de bande amateur) et sont balayables par les touches 1 et 4. 8.5. Variation du niveau : Elle s'effectue en pressant sur la touche F, le niveau s'incrÃĐmente, la touche E produit l'effet inverse. La valeur relative de l'amplitude de sortie est renseignÃĐe sous forme d'un bargraph sur la ligne infÃĐrieure de l'afficheur LCD. 9. INFLUENCE DU COEFFICIENT DE MULTIPLICATION : L'utilisation de la partie multiplicateur du DDS et de ses 17 facteurs de multiplication, apporte incontestablement une souplesse dans le choix de la frÃĐquence d'horloge et de l'oscillateur permettant de la gÃĐnÃĐrer. En effet, pour un mÊme oscillateur de rÃĐfÃĐrence, il sera thÃĐoriquement possible d'obtenir 17 valeurs diffÃĐrentes d'horloge si l'on respecte par ailleurs les contraintes de frÃĐquence maximale et de tempÃĐrature comme ÃĐvoquÃĐes prÃĐcÃĐdemment. Cependant, l'expÃĐrience montre que le facteur de multiplication a une incidence non nÃĐgligeable sur la puretÃĐ spectrale du signal de sortie du DDS. Ceci s'explique par l'architecture du DDS qui lui-mÊme utilise un circuit PLL pour la multiplication. Nous avons comparÃĐ les deux signaux de sortie d'un DDS travaillant avec une frÃĐquence d'horloge de 200 MHz gÃĐnÃĐrÃĐe l'un par un oscillateur de 10 MHz et multiplication par 20, l'autre par un oscillateur de 50 MHz et multiplication par 4. Les rÃĐsultats sont ÃĐvidents à la vue des spectres (voir version anglaise de l'article)et en faveur de la multiplication par 4. Le choix effectuÃĐ pour le montage dÃĐcrit ici est tout à fait convenable (F=40 MHz, k=5) On veillera donc dans la mesure du possible a utiliser un faible coefficient de multiplication ou mieux encore à utiliser un oscillateur fournissant directement la frÃĐquence d'horloge du DDS, ce qui peut ne pas Être trÃs facile si l'on vise les 300 MHzâ? A frÃĐquence d'horloge constante, seul le coefficient de multiplication sera à mettre à jour dans le logiciel. 10. COMPARAISON AVEC LES DDS AD9835/AD9850 Rappelons que la diffÃĐrence principale entre le DDS AD9852 et les DDS AD9835 et AD9850 est la rÃĐsolution du DAC (12 bits au lieu de 10 bits) et la frÃĐquence maximale de l'horloge de rÃĐfÃĐrence. Comparaison 1 : La comparaison a ÃĐtÃĐ tout d'abord rÃĐalisÃĐe avec une frÃĐquence d'horloge identique pour les deux DDS AD9850 et AD9852. La frÃĐquence du signal de sortie a ÃĐtÃĐ fixÃĐ Ã la valeur maximale recommandÃĐe soit 32 MHz (40% F Clock). Les deux spectres ci-contre couvrent chacun la mÊme largeur de bande soit 500 kHz. La diffÃĐrence est ÃĐvidente : l'AD9852 prÃĐsente un pied de spectre sans raie parasite significative vis à vis de l'AD9850 dont les raies parasites atteignent -50 dB par rapport à la frÃĐquence gÃĐnÃĐrÃĐe. Comparaison 2 : Cette fois, le DDS AD9852 est attaquÃĐ par une horloge à 200 MHz, ce qui correspond davantage à son mode nominal de fonctionnement, la frÃĐquence du signal de sortie est toujours de 32 MHz. Le gain en pied de spectre est notable, aucune raie parasite n'est dÃĐcelable. 11. CONCLUSION : Il y a seulement trois ou quatre annÃĐes, j'ignorais tout des DDS. Le temps à passÃĐ, la route a ÃĐtÃĐ longue et semÃĐe d'embÃŧches mais les rÃĐsultats sont encourageants. Je ne peux que souhaiter faire ÃĐcole et inciter le plus grand à expÃĐrimenter et rÃĐaliser ses projets. Je reste à l'ÃĐcoute à F6EHJ@wanadoo.fr 12. COMPOSANTS : 12.1. LISTE DES COMPOSANTS Design: HAM-GENE V9852 Doc. no.: V0 Revision: 1.0 Author: F6EHJ - GÃĐrard LAGIER Created: 20/06/02 Modified: 18/03/03 QtÃĐ RÃĐfÃĐrence VALEUR --- --------- ----- Resistances CMS 1206 --------- 1 R1,R10 3.9K 3 R3,R15,R64 4.7k 5 R2,R4,R5,R6,R7 50 ohms 2 R8,R13 6.8 K 1 R9,R14 10k 2 R11,R12 150 ohms 1 R16 1.3K 4 R60,R61,R62,R63 10K 8 R65,R66,R67,R68,R69,R70,R71, 2.2k R72 Condensateurs tous CMS 1206 sauf indication contraire ---------- 13 C1,C5,C7,C8,C9,C10,C11,C12, 1nF C13,C14,C15,C16,C19 1 C2 27pF 1 C3 47pF 15 C4,C21,C25,C36,C37,C39,C40 C41,C42,C43,C60,C63,C66,C67 10nF C68 1 C6 39pF 1 C17 2.2pF 2 C18,C23 47ÂĩF/10V 3 C20,C29,C30 22ÂĩF/16V 1 C22 12pF 3 C26,C27,C28 100nF 1 C33 22pf 1 C34 8.2pF 2 C61,C62 20pF 3 C31,C32,C35 A dÃĐfinir selon frÃĐquence filtre Circuits IntÃĐgrÃĐs ------------------- 1 U1 AD9852 AST ou ASQ Analog Device 1 U2 AD9835 (option) 1 U3 Oscillateur TTL 40MHz (rÃĐcupÃĐration) 1 U4 LM1085IT-3.3V ou similaire 1 U5 7805 2 U6,U7 en option MSA 2643 HP-Agilent ou similaire 1 U60 PIC16F877-20 Microchip Diodes ------ 4 D60,D61,D62,D63 1N4148 1 D64 1N4001 Divers ------------- 2 J1,J4 en option SUBCLIC ou BNC 1 J2 Cosse 1 J3 Cosse 1 J60 Connecteur SIL 4 (rÃĐcupÃĐration) 2 J61,J62 Connecteur mÃĒle pour CI 10 broches 1 L1 82nH 2 L2, L3 68nH 2 L4 et L5 en option Selon frÃĐquence filtre 1 Quartz 20MHz (pas de criticitÃĐ) 1 plaque ÃĐpoxy simple face 35Âĩm 130X190mm 12.2. APPROVISIONNEMENT : DDS AD9852 : On peut trouver sur le web quelques fournisseurs de ce composant (http://www.sander-electronic.de à 70 Euros environ). Le plus simple et le plus ÃĐconomique est de faire une demande d'ÃĐchantillons gratuits sur le site d'Analog Device. - CMS : Selectronic (boÃŪte d'une cinquantaine de valeurs), RadioSpareâ?. - Oscillateur 40 MHz : JMB electronic, Selectronic, Radiospareâ?.. - PIC 16F877-20 : JMB pour le meilleur prix et le service. - Quartz 20 MHz : JMB/Selectronicâ?.. - Tores : Cholet composant - Subclic/BNC : Cholet Composant - MSA 2643 : Radio Spare (par 5 unitÃĐs) - Connecteur : Comptoir du Languedoc, Radio Spare, Selectronic, Conradâ?. - Epoxy : Attention à la qualitÃĐâ? Le reste des composants est trÃs courant. 13. BIBLIOGRAPHIE ET ADRESSES: Logiciel de CAO PROTEUS : www.multipower.fr Data sheet AD 9852 Analog Device Rev B www.analog.com Article revue MÃĐgahertz Data sheet PIC16F877 www.microchip.com A DDS Project by Jouni Verronen OH8RO http://www.netppl.fi/~jonverro/ Experiments with an Analog Devices AD9852 DDS. http://www.qsl.net/pa3ckr/ad9852/ by PA3CKR Charlos Potma |